N

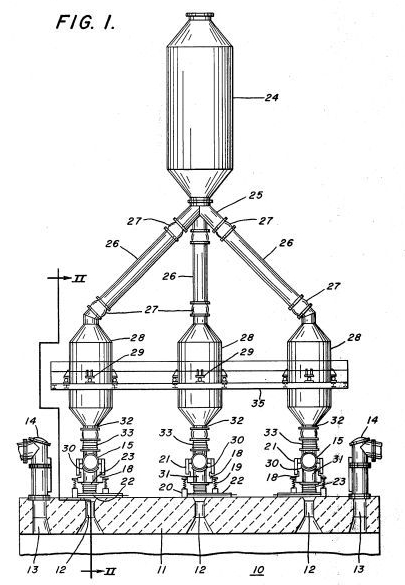

Charging apparatus is provided for charging preheated coal into

a battery of coke oven chambers from a bunker above the battery

which has sufficient capacity to contain enough coal to charge at

least one oven chamber. Each oven chamber has a plurality of

charging holes in the roof and the charging holes of the several

chambers are arranged in rows extending longitudinally of the

battery. A vibratory conveyor is associated with each row of

charging holes for selectively delivering coal to the holes, and

coal is supplied from the bunker to each conveyor through a

measuring chamber which holds a predetermined amount of coal and

delivers exactly the right amount to the conveyor for charging one

oven chamber.

W

A semiconductor memory IC including an address value register,

an adder and an address difference signal line, wherein an address

for operation of the semiconductor memory IC is specified by an

address difference signal representing an increment/decrement of

the address value register An optional address can be specified by

an increment/decrement signal, and all memory cells can be

addressed even though the number of terminals is smaller than that

required for specifying an absolute value of an address, so that

the semiconductor memory IC can be reduced in size. To form a

semiconductor memory device by using this semiconductor memory IC,

an address memory unit, an address value difference computing unit

and an addressing unit are provided. When operating the memory

device, a target address in the memory unit can be reached by

specifying a difference between the target address and the address

held in the address memory unit.

+

An SRAM adapted for changing the sequence of data. A counter 7

generates a sequentially increasing address signal. A write

designation circuit 2a sequentially designates a memory cell row to

be selected for writing in response to the address signal.

Conversely, a read designation circuit 3a designates a memory cell

row in response to the address signal in a sequence determined by a

predetermined rule. The generation of an address signal, which

changes in a complicated manner and is required for changing the

sequence of data, is not required, so that the amount of the

operation process by the CPU is decreased.

You can check your answers for this puzzle on

Geochecker.com.